以下文章来源于昇和影音集团 ,作者昇和影音集团

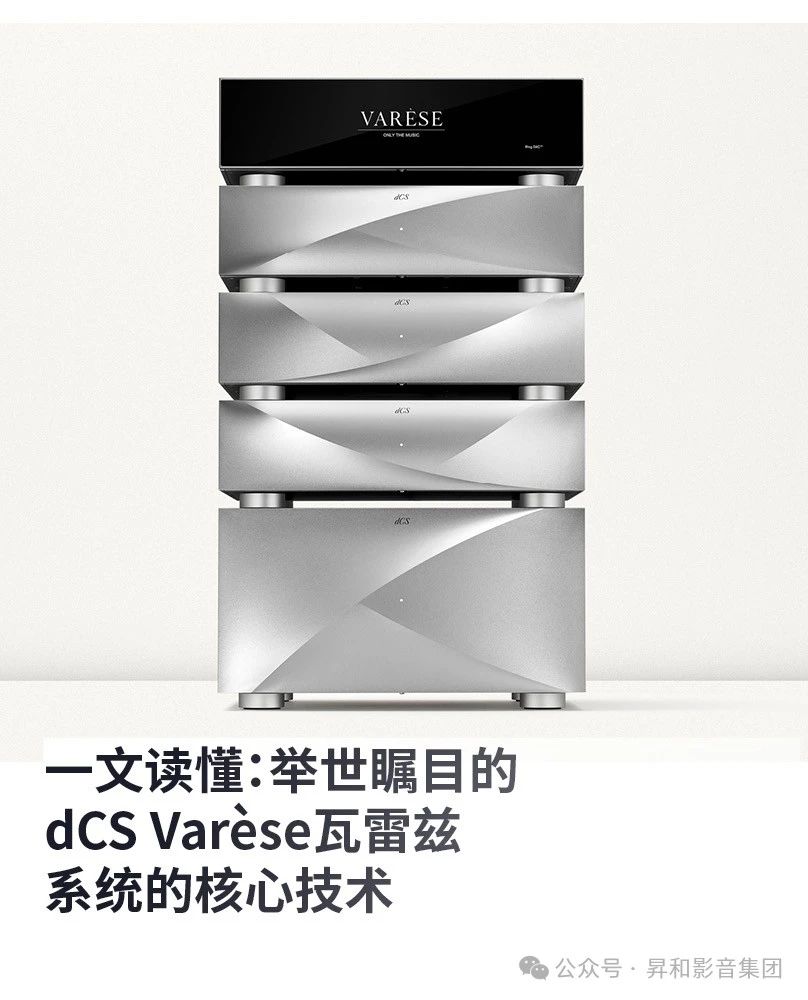

历经5年研发、推翻一切旧观念、创造未来之巅的英国dCS Varèse瓦雷兹数码音频播放系统,已经在举世瞩目下耀目登场。毫无疑问,dCS用令人惊讶的方式,再次大幅拔高了原本就由自己创造的数码音频高度,Varèse瓦雷兹的发布,宣告了这是一套由崭新理念与领先技术的完美融合,将数码音乐重播带到了前所未有新纪元的旗舰产品。

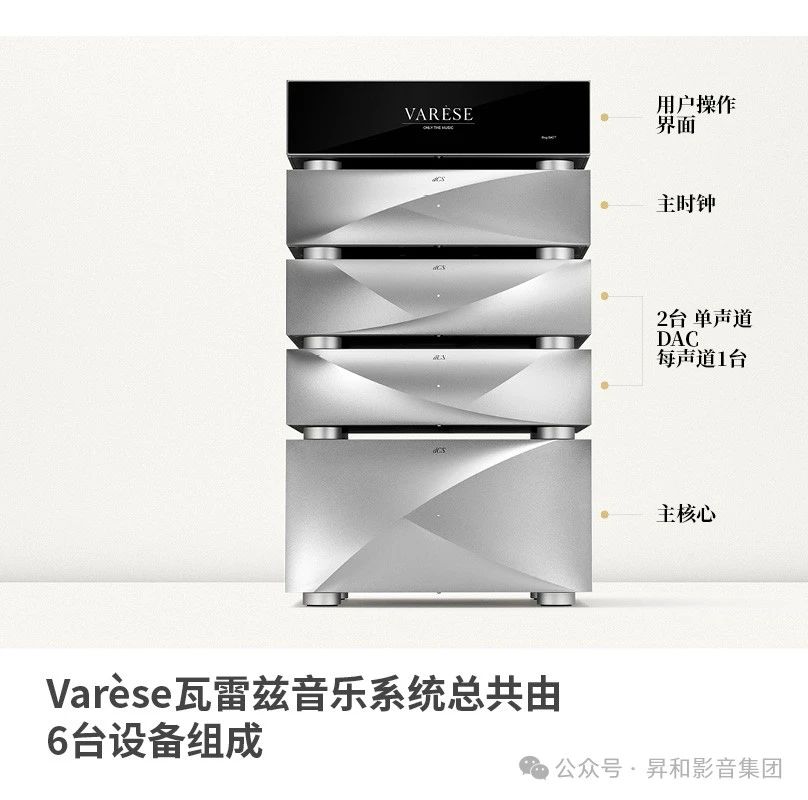

Varèse瓦雷兹音乐系统总共由6台设备组成:

Varèse Core 主核心

Varèse Mono Ring DAC(2台单声道解码器,每声道1台)

Varèse User Control 用户操作界面

Varèse Master Clock 主时钟

Varèse CD/SACD Transport 转盘(将于2024年底左右另行发布)

另外,还包括1个专用无线遥控器,配备相应的专利技术ACTUS接线,及崭新的应用程序:dCS Mosaic ACTUS 。

超越自我的Varèse Mono Ring DAC

Varèse瓦雷兹系统的设计始于DAC的性能革新,创造性地以差动技术开发出Varèse Mono Ring DAC单声道数模转换器。dCS Ring DAC解码器的标志性声音特征是精湛的低失真,这一点至关重要,即使在低讯号电平下也是如此——这是大多数其他DAC架构所不足的领域。这种卓越的超低失真性能依靠dCS从底层自研的自家Ring DAC(环形数模转换器),通过自主编写的FPGA及独特的电流源阵列结构,带来了远超市面是现成DAC芯片的性能和声音表现。事实上,Ring DAC本身极低的残余杂讯水平,其中绝大多数杂讯已远远超出了人耳可闻频率范围,因此可以通过DAC输出上温和的模拟滤波器轻松消除。

在第三代Ring DAC(APEX版本)中,每台双声道Ring DAC均由96个电流源组成单端技术的Ring DAC线路,其中48个用于左声道,另外48个用于右声道,构成左右声道DAC线路板。每个电流源产生相等的电压,并用于将这些电流源中的任何分量误差(电阻值容差)作为随机噪声进行分配。总共96个电流源组成的。

在Varèse瓦雷兹系统中,左声道和右声道被独立成为“Mono DAC单声道数模转换器”,每个声道独立为一台完整的DAC设备。并且在线路技术上进行了许多重大的改进,当中包括了一些dCS专有技术。每台Varèse Mono DAC均内含了完整的96个电流源,这意味着每个音频通道使用的电流源数量是第三代Ring DAC产品的两倍。这些电流源提供同步调变为5.644MHz或6.144MHz(取决于音源内容取样率)的5Bit(位元)PCM 信号。

Varèse瓦雷兹的Ring DAC在差动架构中工作;Ring DAC线路板上的96个电流源分为两组,每组48个,其中一组以正半波转换音乐信号,第二组48个电流源负半波转换音乐信号。这意味着反相位电流源的相位是反转的,并与正相位电流源相加,并且有效抵消了信号的噪音和失真,从而达到更优秀的性能和声音表现。与第三代Ring DAC已经非常出色的性能相比,以这种差动方式运行Ring DAC的效果提供了许多性能增强。

差动技术的优势:

1.平衡参考电源的电流消耗。

电源基准电压输入到电流源,无论接通多少电流源,该电压都会乘以电流源。除了输入电流源的清洁直流电之外,其他任何东西也会成倍增加,其中Ring的正相位侧处于较高电压,而负相位侧处于较低电压。这意味着基准电源的消耗与信号无关,因为两组电流源工作互补。从而消除了Ring DAC线路产生二次谐波的机制,改善了失真性能。

2. 改进Ring DAC内的偶次谐波性能。

dCS自研的Mapper映射算法规定了Ring DAC中的哪些电流源针对特定数字音频信号开启和关闭,导致正半波和负半波上的电流源产生不等量的开关噪音(正半波和负半波意味着Ring DAC在输出端分别再生正电压或负电压)。两个反相环的差动工作可以均衡信号正反相位的这种不对称性,从而实现更优秀的线性度。

3.均衡每个总和节点上的偏移,从而消除了显式直流偏移校正的需要,并提高了总和/滤波器电路的对称性。

4.现有的dCS DAC采用多块不同功能的线路板来执行D/A转换过程的不同功能,而Varèse Mono DAC则采用单一的一体化线路板涵盖了所有数字处理和模拟音频的功能。这在许多设计方面进行了改进,并提高了Varèse Mono DAC性能的一致性。

在Varèse瓦雷兹系统中,双单声道DAC(每台都运行差动Ring DAC 架构)的工作方法,能够将dCS标志性的超低失真声音推向新的性能高度,同时将本底噪声降低3dB。Ring DAC APEX已经处于数字模拟转换技术的前沿,而Varèse瓦雷兹的差动Ring DAC继续大大拉开这一差距。

电源供应的改进

Ring DAC采用输送到所有电流源的参考电压,并将其乘以一个通过映射器输送的数字音频代码样本,该映射器指示在任何给定时间需要打开哪些电流源以在输出端产生正确的电压,这意味着DAC内部的基准电压对系统性能至关重要。尤其对于Ring DAC这样具有揭示性和透明度的技术架构,包括供电在内的任何技术细节比其它任何方案都更为重要。比如:在以往采用立体声设计的Ring DAC中,通过比较左右声道在不同的时间打开和关闭不同数量的电流源会发现。当电流源接通和关断时,它们相对于基准电源的阻抗会发生变化,这可能会对基准电源产生波纹效应,从而影响系统的音质。APEX在此基础上进行了改进,通过降低将基准电压输送到Ring DAC电流源的信号路径的阻抗,使系统能更彻底抵抗电流源开关和基准电源之间的这些相互作用。

在Varèse瓦雷兹差动Ring DAC设计中,正反半波的电流源会以相同的方式彼此运行,因为两组电流源都再现相同的音乐信号(其中一组相位反相),基准电压的消耗在两者之间是相同的。这意味着基准电压在工作时保持更加稳定,这对于像Ring DAC这样的乘法DAC来说,对音乐性能有巨大的影响。

与目前的dCS产品相比,构成Varèse瓦雷兹系统电源的硬件得到了改进:Rossini和Vivaldi系统的Ring DAC采用双电源变压器,DAC的模拟和数字线路均由单独的变压器供电,从而提高了性能,并且降低了内部的干扰。Varèse Mono DAC毫无保留配备了双变压器,而且每个变压器都针对其在模拟或数字电源中的使用进行了专门优化,从而提高了Mono DAC的性能和声音重播水平。其中电源次级电路经过重新设计,以减少变压器铁芯中的磁隙伸缩效应,从而消除了变压器可能产生的噪声。电源稳压器采用不同的拓扑结构,电源时序通过电源管理IC实现,以实现对电源激活和停用的更严格、更灵活的控制。为模拟信号平衡输出级供电的电源,也额外设计了更强大的稳压和滤波线路,以进一步降低共模噪声,从而提高模拟音频线路的性能。

创新的ACTUS技术

在一个理想的音乐系统中,每台设备都能够与系统中的其他组件进行通信,从而允许在它们之间发送重要信息和命令,使系统能够作为一个整体运行。使用Vivaldi,这是通过两种主要机制实现的:3路RS232互连,将DAC和转盘连接到升频器,以及通过双AES接口连接。通过利用RS232连接并发送嵌入在双AES线材连接中的隧道命令,从DAC到升频器,以及从转盘到升频器,Vivaldi系统能够无缝控制每个组件的设置、音量控制、选择信号源等,音频信号也通过双AES同步发送。

但新的Varèse瓦雷兹系统打破了以往的观念。Varèse瓦雷兹采用由dCS自家开发的定制界面,可实现更好的音频重播质量——结合用户对整套系统无缝控制的预期。该接口称为:ACTUS,音频控制和时钟统一系统。ACTUS由dCS研发的专有硬件和软件技术组合而成,允许Varèse瓦雷兹系统每部设备(核心、用户界面、时钟、单声道DAC)通过各自单根线材连接到核心,包括异步数字音频、控制信号和主时钟信号(通过获得专利的Tomix时钟技术发送),都由一根ACTUS线材完成连接。

Varèse Core主核心作为系统的枢纽,所有其他Varèse瓦雷兹设备都通过ACTUS线材连接到该核心。连接器是有定位键的,这意味着它只能以正确的方式插入。这条线材本身是无方向性的,可以在系统中的任何位置使用,这使得使用ACTUS线材设置Varèse瓦雷兹系统变得非常简单。ACTUS界面的唯一具体要求是Varèse主时钟必须连接到Varèse Core主核心上标注「Clock」的ACTUS插座。

ACTUS线材由6条双绞铜线组成,执行以下任务:

1根双绞线传输48k Tomix信号

4根双绞线形成IP(互联网协议)连接链路

IP链路将每台Varèse瓦雷兹设备连接到Varèse Core主核心。此IP链路使系统具有完全控制权,允许在设备之间无缝发送信息、设置更改和其他控制信息,而无需额外的控制接口。这种控制级别对于系统故障查找也非常有用,例如,系统能够智能地通知用户左声道DAC未得到纠正,或者时钟连接到Varèse Core主核心上的错误ACTUS端口等等。

IP链路还负责在Varèse瓦雷兹设备之间传输音频信号。ACTUS不再使用以往的AES3或S/PDIF等同步接口,而是利用IP通过异步纠错接口发送音频,这意味着不存在时基或数据完整性错误的可能性。请注意,ACTUS不使用既定的行业标准通过IP发送音频,例如AES67。

Varèse Core核心与单声道DAC处理

对于旗舰dCS系统,长期以来一直使用升频器,这是与DAC独立分离的一台外置设备,它执行超采样过程中所需的大部分数/数转换、滤波和DSP。这是dCS从开发专业设备的工作中发现的,将大量处理工作从DAC中脱离出来,成为独立外置设备,可显著提升效能。

Varèse Core主核心负责处理这些元素中的大部分任务,将DAC与必须使用的大部分数字处理工作负载脱离开。这意味着大幅减少DAC内部的FPGA的工作量,让DAC工作更轻松。这意味着电源的串扰影响更少,从而进一步提升了单声道DAC的性能。Varèse Core主核心接收任何传入的PCM源数据,并将其超采样至705.6或768kS/s,对信号进行数字滤波以去除Nyquist奈奎斯特图像。然后,用户可以在播放PCM源数据时选择可选的DSD模式。此模式将信号转换为DSD(从标准DSD/64到DSD/512)。然后,这种超采样、滤波的数字音频信号通过ACTUS传送到单声道DAC,并被调制为5Bit ~6MHz信号,然后输送到Ring DAC进行数/模转换。

单声道DAC时钟的问题

在时钟方面,让两台单声道DAC如何能够协调精准在同一时基上工作是相当具挑战性的工作。在以立体声DAC设计的传统数码音频系统中,DAC内部就具有产生时钟信号的电路。该时钟信号同时传输到DAC的左右声道,这意味着两个声道同时将数字音频样本转换为模拟电压。但是,在单声道DAC工作时,DAC的所有电路都在左右声道之间分配。

如果两部单声道DAC不能时间同步转换左右声道的数据,将出现显著且无法接受的音频质量下降。为确保数据同时转换,两台DAC都需要确保其时钟信号在左声道DAC和右声道DAC具有上升沿(构成时钟信号的方波变化,其中电压从低态(如0V)变为高态(如5V))时间上保持严格的对齐。

但这还不够。即使左右声道DAC上的两个时钟信号具有完全对齐的上升沿,但是每台DAC并非都转换相同的数据,出现这种情况同样会严重损害音质。因此,在时钟方面,两个DAC必须精确对齐,两个时钟同时产生一个上升沿,并用这个同步的时钟信号转换相同的数据。而且,目前音频行业的解决方案(AES/S-PDIF信号同步设备)并没有足够的频宽来满足Varèse瓦雷兹所需的方式工作。另一种名为AES 67的替代方案虽然有足够的频宽,但却需要额外的时间伺服器从网络时钟重建其时钟。因此,该时钟信号的精确度性能还不如使用DAC内部的音频速率石英晶体振荡器生成的物理时钟所建立的本地时钟信号。

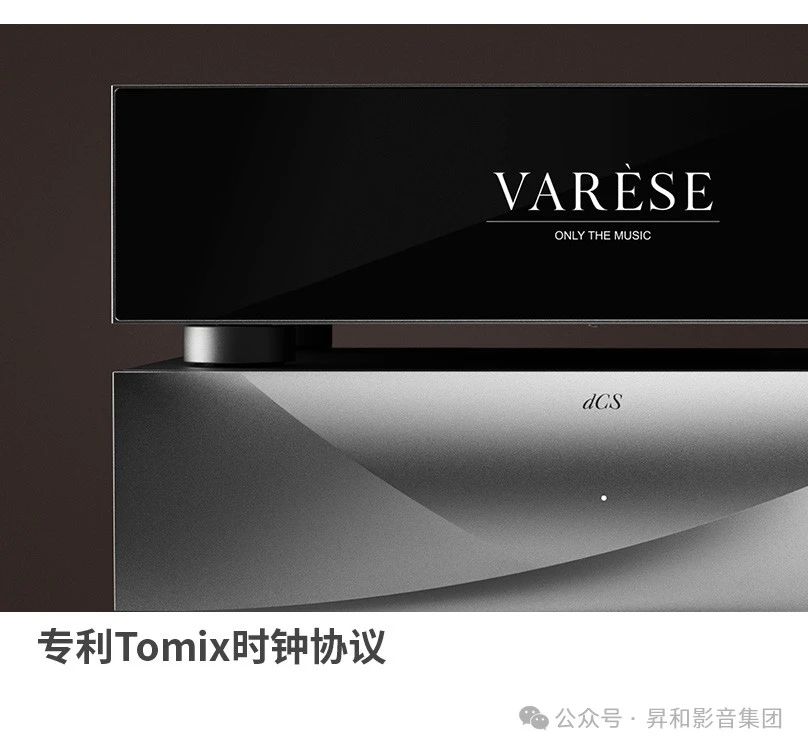

专利Tomix时钟协议

为了彻底解决以上问题,dCS决定创建一种新的方法来紧密同步两台单声道DAC的时钟,同时利用每台DAC内部基于VCXO(压控晶振元件)的本地高质量时钟电路来控制各自的Ring DAC电路,从而更大限度地提高系统。从而诞生的解决方案是Tomix时钟协议。

Tomix是一种定制的专利方案,Varèse Core主核心的作用与传统音频系统中的主时钟大致相同。它将时钟信号发送到两个单声道DAC上,它们会同步这两个单声道DAC,从而确保DAC时钟以相同的速率运行。然而,这本身并不能解决保持D/A转换同步的问题。

Core是Varèse瓦雷兹系统的中心,任何音频和时钟信号始终通过它:无论源、系统配置和设置如何。在通过ACTUS将数码音频数据发送到DAC之前,Core会为通过它的每个音频数据添加一个时间戳。当数据到达DAC时,DAC内的FPGA会显示时间戳。然后,DAC确切地知道数据的发送时间,但为了确保在正确的时间将数据转换为模拟信号,它还需要确切知道当前的时间基准。这就是Tomix时钟协议的用武之地。时钟信号加盖时间戳的方法对音频性能至关重要。Tomix信号由Varèse主时钟生成,或者如果系统中未使用主时钟,则由Varèse Core主核心产生。技术的成果令人欣喜,Tomix时钟协议是dCS一种获得专利的技术,让Varèse Mono DAC具有精确同步的时钟,确保单声道Ring DAC在完全相同的时间转换左声道和右声道的音频数据。

联系地址 :广州市越秀区明月一路

联系电话 :020-8358157

传真号码 :020-8358385

微信公众号

视频号